# Thesis for the degree of Doctor of Technology Sundsvall 2008

# Memory Synthesis for FPGA Implementation of Real-Time Video Processing Systems

### Najeem Lawal

Supervisors: Professor Mattias O'Nils

Professor Bengt Oelmann Doctor Benny Thörnberg

Electronics Design Division, in the Department of Information Technology and Media Mid Sweden University, SE-851 70 Sundsvall, Sweden

ISSN 1652-893X Mid Sweden University Doctoral Thesis 66

ISBN 978-91-86073-26-8

Akademisk avhandling som med tillstånd av Mittuniversitetet i Sundsvall framläggs till offentlig granskning för avläggande av teknologie doktors examen i elektronik onsdagen den 07 Jan 2009, klockan 10:30 i sal O102, Mittuniversitetet Sundsvall. Seminariet kommer att hållas på engelska.

# Memory Synthesis for FPGA Implementation of Real-Time Video Processing Systems

Najeem Lawal

© Najeem Lawal, 2009

Electronics Design Division, in the Department of Information Technology and Media Mid Sweden University, SE-851 70 Sundsvall Sweden

Telephone: +46 (0)60 148561

Printed by Kopieringen Mittuniversitetet, Sundsvall, Sweden, 2009

#### **ABSTRACT**

In this thesis, both a method and a tool to enable efficient memory synthesis for real-time video processing systems on field programmable logic array are presented. In real-time video processing system (RTVPS), a set of operations are repetitively performed on every image frame in a video stream. These operations are usually computationally intensive and, depending on the video resolution, can also be very data transfer dominated. These operations, which often require data from several consecutive frames and many rows of data within each frame, must be performed accurately and under real-time constraints as the results greatly affect the accuracy of application. Application domains of these systems include machine vision, object recognition and tracking, visual enhancement and surveillance.

Developments in field programmable gate arrays (FPGAs) have been the motivation for choosing them as the platform for implementing RTVPS. Essential logic resources required in RTVPS operations are currently available and are optimized and embedded in modern FPGAs. One such resource is the embedded memory used for data buffering during real-time video processing. Each data buffer corresponds to a row of pixels in a video frame, which is allocated using a synthesis tool that performs the mapping of buffers to embedded memories. This approach has been investigated and proven to be inefficient. An efficient alternative employing resource sharing and allocation width pipelining will be discussed in this thesis.

A method for the optimised use of these embedded memories and, additionally, a tool supporting automatic generation of hardware descriptions language (HDL) modules for the synthesis of the memories according to the developed method are the main focus of this thesis. This method consists of the memory architecture, allocation and addressing. The central objective of this method is the optimised use of embedded memories in the process of buffering data on-chip for an RVTPS operation. The developed software tool is an environment for generating HDL codes implementing the memory subcomponents.

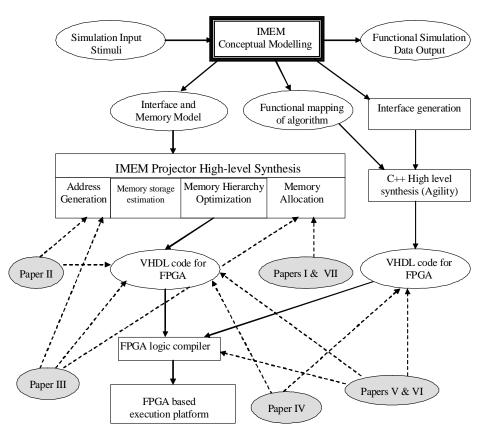

The tool integrates with the Interface and Memory Modelling (IMEM) tools in such a way that the IMEM's output - the memory requirements of a RTVPS - is imported and processed in order to generate the HDL codes. IMEM is based on the philosophy that the memory requirements of an RTVPS can be modelled and synthesized separately from the development of the core RTVPS algorithm thus freeing the designer to focus on the development of the algorithm while relying on IMEM for the implementation of memory sub-components.

#### **SAMMANDRAG**

I denna avhandling presenteras en metod och ett verktyg för möjliggörandet av effektiv minnessyntes för vidoebearbetande system i realtid på Field Programmable Gate Array (FPGA). I ett system som bearbetar video i realtid (RTVPS) upprepas en mängd processer i varje bildruta i en videosekvens. Dessa processer är ofta beräkningsintensiva och, beroende på videoupplösningen, kan de också vara mycket dataöverföringsstyrda. Processerna, som ofta kräver data från en mängd konsekutiva bildrutor och många dataserier inom varje ruta, måste genomföras exakt och under realtidsbegränsningar, då resultaten i hög grad påverkar tillämpningens exakthet. Tillämpningsområden för dessa system innefattar igenkänning av föremål, spårning av föremål samt övervakning.

Utvecklade produkter inom FPGA har motiverat användandet av dessa som plattform för tillämpning av RTVPS. De nödvändiga logikresurser som krävs för RTVPS-processer är för tillfället tillgängliga, optimerade och inbyggda i modern FPGA. En sådan resurs är det inbyggda minne som används för datalagring under videoprocessning i realtid. Varje datalager motsvarar en rad pixlar i en videoruta som automatiskt allokeras på FPGAs. Denna metod har undersökts och visat sig vara effektiv. Ett effektivt alternativ som utnyttjar resursdelning och anslag vid rörledning diskuteras i denna avhandling.

En metod för optimal användning av dessa inbäddade minnen och ett verktyg som stöder automatisk generering av HDL-koder för minnessyntes enligt den utvecklade metoden är fokus för denna avhandling. Denna metod består av minnesarkitektur, allokering och adressering. Metodens centrala mål är optimal användning av inbäddade minnen under lagring av data på chip för en RTVPS-operation. Den utvecklade mjukvaran är en miljö för att generera HDL-koder, där minneskomponenter tillämpas.

Verktyget integreras med IMEM-verktyg (Interface and Memory Modelling) på ett sådant sätt att IMEM:s utdata – minneskraven för ett RTVPS, importeras och behandlas för att generera HDL-koderna. IMEM baseras på filosofin att minneskraven för ett RTVPS kan modelleras och syntetiseras separat från utvecklandet av den ursprungliga huvudalgoritmen för RTVPS och därigenom ge designern frihet att fokusera på utvecklingen av algoritmen, medan IMEM används för tillämpning av minneskomponenter.

#### **ACKNOWLEDGEMENTS**

First of all I would like to show my great appreciation of my supervisors Prof. Mattias O'Nils, Prof. Bengt Oelmann and Dr. Benny Thörnberg for their academic and scientific guidance and inspirations, and for giving me the opportunity to study for Ph.D. Prof. Hans-Erik Nilsson and Dr. Jerzy Kirrander are greatly acknowledged for their contributions and inspirations. I am grateful to Fanny Burman and Lotta Söderström for their kind support. I would also like to thank all my colleagues at the Mid Sweden University, my friends and my family for their supports.

I would also like to express my gratitude to the Mid Sweden Unviersity, the Swedish KK foundation and ARTES Graduate School for their financial supports.

Sundsvall, Jan 2009

Najeem Lawal

### TABLE OF CONTENTS

| SAMMANDRAG         V           ACKNOWLEDGEMENTS         VI           TABLE OF CONTENTS         IX           ABBREVIATIONS AND ACRONYMS         XIII           LIST OF FIGURES         XV           LIST OF TABLES         XVI           LIST OF PAPERS         XIX           1 INTRODUCTION         1           1.1 REAL-TIME VIDEO PROCESSING SYSTEM         1           1.2 IMPLEMENTATION ALTERNATIVES         4           1.2.1 Application Specific Integrated Circuits         4           1.2.2 Software Based Processors         4           1.2.3 Programmable Hardware Processors         4           1.2.1 Application Specific Integrated Circuits         9           1.3 DATA REQUIREMENTS IN RTVPS         6           1.4 MOTIVATION FOR EFFICIENT MEMORY SYNTHESIS         9           1.5 PROBLEM DESCRIPTION         10           1.6 PERFORMANCE COMPARISON         11           1.6.1 Experimental Set-Up         11           1.6.2 Results         12           1.7 MAIN CONTRIBUTIONS         14           1.8 THESIS OUTLINE         14           2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)         15           2.1.1 Programmable Interconnects         17           2.1.3 On-chip RAM Block | ABSTRACT                                                                                                        |                                                                                                                                                                                                                                                                                         | III            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| ABBREVIATIONS AND ACRONYMS XIII  LIST OF FIGURES XVI  LIST OF TABLES XVI  LIST OF PAPERS XIX  1 INTRODUCTION 1  1.1 REAL-TIME VIDEO PROCESSING SYSTEM 1  1.2 IMPLEMENTATION ALTERNATIVES 4  1.2.1 Application Specific Integrated Circuits 4  1.2.2 Software Based Processors 4  1.2.3 Programmable Hardware Processors 4  1.3 DATA REQUIREMENTS IN RTVPS 6  1.4 MOTIVATION FOR EFFICIENT MEMORY SYNTHESIS 9  1.5 PROBLEM DESCRIPTION 10  1.6.1 Experimental Set-Up 11  1.6.2 Results 12  1.6.3 Conclusion 13  1.7 MAIN CONTRIBUTIONS 14  1.8 THESIS OUTLINE 14  2 FIELD PROGRAMMABLE GATE ARRAY (FPGA) 15  2.1.1 Programmable Logic Cells 15  2.1.2 Programmable Interconnects 17  2.1.3 On-chip RAM Block 19  2.1.4 Embedded cores 19  3 RELATED WORKS 22  3.1.1 Abstraction level 21  3.1.2 Design verification 22  3.1.3 Resource usage 22                                                                                                                                                                                                                                                                                                                                                                       | SAMMANDE                                                                                                        | RAG                                                                                                                                                                                                                                                                                     | V              |

| ABBREVIATIONS AND ACRONYMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ACKNOWLE                                                                                                        | EDGEMENTS                                                                                                                                                                                                                                                                               | VII            |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TABLE OF (                                                                                                      | CONTENTS                                                                                                                                                                                                                                                                                | IX             |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ABBREVIAT                                                                                                       | TIONS AND ACRONYMS                                                                                                                                                                                                                                                                      | XIII           |

| LIST OF PAPERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                 |                                                                                                                                                                                                                                                                                         |                |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                 |                                                                                                                                                                                                                                                                                         |                |

| 1.1       REAL-TIME VIDEO PROCESSING SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |                                                                                                                                                                                                                                                                                         |                |

| 1.2       IMPLEMENTATION ALTERNATIVES       4         1.2.1       Application Specific Integrated Circuits       4         1.2.2       Software Based Processors       4         1.2.3       Programmable Hardware Processors       4         1.3       DATA REQUIREMENTS IN RTVPS       6         1.4       MOTIVATION FOR EFFICIENT MEMORY SYNTHESIS       9         1.5       PROBLEM DESCRIPTION       10         1.6       PERFORMANCE COMPARISON       11         1.6.1       Experimental Set-Up       11         1.6.2       Results       12         1.6.3       Conclusion       13         1.7       MAIN CONTRIBUTIONS       14         1.8       THESIS OUTLINE       14         2       FIELD PROGRAMMABLE GATE ARRAY (FPGA)       15         2.1.1       Programmable Logic Cells       15         2.1.2       Programmable Interconnects       17         2.1.3       On-chip RAM Block       19         2.1.4       Embedded cores       19         3       RELATED WORKS       21         3.1.1       Abstraction level       21         3.1.2       Design verification       22         3.1.3       Re                                                                                           | I INTROI                                                                                                        | DUCTION                                                                                                                                                                                                                                                                                 | 1              |

| 2.1.1 Programmable Logic Cells       15         2.1.2 Programmable Interconnects       17         2.1.3 On-chip RAM Block       19         2.1.4 Embedded cores       19         3 RELATED WORKS       21         3.1 CHALLENGES IN SYSTEM DEVELOPMENT ON FPGA       21         3.1.1 Abstraction level       21         3.1.2 Design verification       22         3.1.3 Resource usage       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.2 IMI<br>1.2.1<br>1.2.2<br>1.2.3<br>1.3 DA<br>1.4 MG<br>1.5 PR<br>1.6 PE<br>1.6.1<br>1.6.2<br>1.6.3<br>1.7 MA | PLEMENTATION ALTERNATIVES  Application Specific Integrated Circuits  Software Based Processors  Programmable Hardware Processors  TA REQUIREMENTS IN RTVPS  OTIVATION FOR EFFICIENT MEMORY SYNTHESIS  OBLEM DESCRIPTION  RFORMANCE COMPARISON  Experimental Set-Up  Results  Conclusion |                |

| 2.1.2       Programmable Interconnects       17         2.1.3       On-chip RAM Block       19         2.1.4       Embedded cores       19         3       RELATED WORKS       21         3.1       CHALLENGES IN SYSTEM DEVELOPMENT ON FPGA       21         3.1.1       Abstraction level       21         3.1.2       Design verification       22         3.1.3       Resource usage       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2 FIELD I                                                                                                       | PROGRAMMABLE GATE ARRAY (FPGA)                                                                                                                                                                                                                                                          | 15             |

| 3.1       CHALLENGES IN SYSTEM DEVELOPMENT ON FPGA       21         3.1.1       Abstraction level       21         3.1.2       Design verification       22         3.1.3       Resource usage       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.1.2<br>2.1.3                                                                                                  | Programmable InterconnectsOn-chip RAM Block                                                                                                                                                                                                                                             | 17<br>19       |

| 3.1.1Abstraction level213.1.2Design verification223.1.3Resource usage22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |                                                                                                                                                                                                                                                                                         |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.1.1<br>3.1.2<br>3.1.3                                                                                         | Abstraction level Design verificationResource usage                                                                                                                                                                                                                                     | 21<br>22<br>22 |

|   | 3.2 DES        | IGN METHODS AND LANGUAGES                                 | 23    |     |

|---|----------------|-----------------------------------------------------------|-------|-----|

|   | 3.2.1          | C/C++ Models                                              | 23    |     |

|   | 3.2.2          | Java Model                                                | 24    |     |

|   | 3.2.3          | MATLAB Model                                              | 24    |     |

|   | 3.2.4          | Hardware Description Model                                | 25    |     |

|   | 3.2.5          | Performance comparison                                    | 25    |     |

|   | 3.3 PRE        | VIOUS WORKS ON ON-CHIP MEMORY SYNTHESIS                   |       |     |

|   | 3.3.1          | Allocation algorithms                                     | 26    |     |

|   | 3.3.2          | Memory addressing                                         |       |     |

|   | 3.3.3          | C++ based System Synthesis                                |       |     |

|   | 3.3.4          | Constraint Generation                                     |       |     |

|   | 3.3.5          | Response to related works                                 |       |     |

| 4 |                | SYNTHESIS FOR REAL-TIME VIDEO PROCESSING                  |       | 24  |

|   | SYSTEM         | S                                                         | ••••• | .31 |

|   | 4.1 IME        | M Synthesis Workflow                                      | 31    |     |

|   |                | L INTEGRATION                                             | 33    |     |

|   | 4.2.1          | Integration with C-Based tools                            | 33    |     |

|   | 4.2.2          | Integration with MATLAB                                   | 34    |     |

|   | 4.2.3          | Integration with Xilinx ISE and ModelSim                  | 34    |     |

|   | 4.3 MEM        | IORY SYNTHESIS ARCHITECTURE                               | 34    |     |

|   | 4.4 MEN        | IORY IMPLEMENTATION                                       | 37    |     |

|   | 4.5 MEM        | IORY ALLOCATION                                           | 38    |     |

|   | 4.5.1          | Allocation algorithm                                      | 38    |     |

|   |                | Definitions                                               |       |     |

|   | 4.5.3          | Proposed algorithm                                        | 42    |     |

|   | 4.5.4          | Complexity analysis                                       | 43    |     |

|   | 4.6 ARC        | HITECTURE DRIVEN BLOCK RAM OPTIMISATION                   | 43    |     |

|   | 4.7 MEN        | IORY ACCESSING                                            | 46    |     |

|   | 4.7.1          | Base Pointer Approach                                     |       |     |

|   | 4.7.2          | Distributed Pointer Approach                              |       |     |

|   |                | STRAINT GENERATION                                        |       |     |

|   |                | ULTS                                                      |       |     |

|   | 4.9.1          | Real-time video processing design cases                   |       |     |

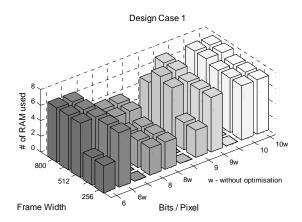

|   | 4.9.2          | Allocation Results                                        |       |     |

|   |                | Performance analysis with varying length and width        |       |     |

|   | 4.9.4          | Performance analysis with varying length and Block RAM 59 |       |     |

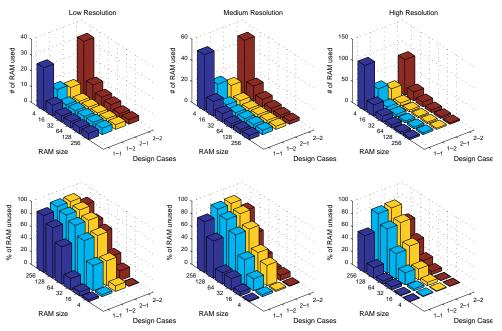

|   | 4.9.5          | Performance Analysis for video processing systems         | 60    |     |

|   | 4.9.6          | Performance of Architecture Driven Memory Allocation      |       |     |

|   | 4.9.7          | Results of the addressing                                 |       |     |

|   | 4.9.8          | Result of Constraint Generation                           |       |     |

| 5 |                | SUMMARY                                                   |       | .67 |

|   | 5.1 MEM        | IORY SYNTHESIS                                            | 60    |     |

|   | 5.1.1          | Paper I                                                   |       |     |

|   | 5.1.1<br>5.1.2 | •                                                         |       |     |

|   | 5.1.2<br>5.1.3 | Paper VIIPaper II                                         |       |     |

|   |                | FORMANCE ANALYSIS                                         |       |     |

|   | J.Z FER        | I UNIVIANUE ANALTOIS                                      |       |     |

|                      | 5.2.1                                    | - F                            |    |                            |

|----------------------|------------------------------------------|--------------------------------|----|----------------------------|

|                      | 5.2.2                                    |                                |    |                            |

| ,                    |                                          | DLS INTEGRATION                |    |                            |

|                      | 5.3.1                                    | Paper V                        |    |                            |

| ,                    |                                          | ST-SYNTHESIS OPTIMISATION      |    |                            |

|                      | <i>5.4.1</i>                             | Paper VI                       | 69 |                            |

| ,                    | 5.5 Aut                                  | THOR'S CONTRIBUTIONS           | 70 |                            |

| 6                    | THESIS                                   | SUMMARY                        | 7  | 71                         |

| (                    | 6.1 Disc                                 | CUSSIONS                       | 71 |                            |

|                      | 6.1.1                                    | Memory architecture            | 71 |                            |

|                      | 6.1.2                                    | Memory allocation              |    |                            |

|                      | 6.1.3                                    | Memory addressing              |    |                            |

|                      | 6.1.4                                    | Boundary conditions management |    |                            |

|                      | 6.1.5                                    | IMEM interfaces                |    |                            |

|                      | 6.1.6                                    | Constraint Generation          |    |                            |

| (                    |                                          | NCLUSIONS                      |    |                            |

|                      |                                          | URE WORKS                      |    |                            |

| _                    |                                          |                                |    | ,_                         |

| 7                    | KEFEKE                                   | NCE                            |    | <b>' D</b>                 |

|                      |                                          |                                |    |                            |

|                      | DENDIV A                                 |                                |    |                            |

| ΑP                   | PENDIX A                                 |                                | 8  | 31                         |

|                      |                                          |                                |    |                            |

|                      |                                          |                                |    |                            |

| PA                   | PER I                                    |                                | 8  | 33                         |

| PA                   | PER I                                    |                                | 8  | 33                         |

| PA<br>PA             | APER I                                   |                                | 10 | 33<br>)7                   |

| PA<br>PA             | APER I                                   |                                | 10 | 33<br>)7                   |

| PA<br>PA             | \PER  <br>\PER                           |                                | 10 | 33<br>07<br>15             |

| PA<br>PA             | \PER  <br>\PER                           |                                | 10 | 33<br>07<br>15             |

| PA<br>PA<br>PA       | APER I<br>APER II<br>APER III<br>APER IV |                                | 10 | 33<br>)7<br>  15           |

| PA<br>PA<br>PA       | APER I<br>APER II<br>APER IV<br>APER V   |                                | 10 | 33<br>07<br>15<br>21       |

| PA<br>PA<br>PA       | APER I<br>APER II<br>APER IV<br>APER V   |                                | 10 | 33<br>07<br>15<br>21       |

| PA<br>PA<br>PA<br>PA | APER I<br>APER II<br>APER IV<br>APER V   |                                | 10 | 33<br>07<br>15<br>21<br>31 |

### **ABBREVIATIONS AND ACRONYMS**

| ALU   | <br>Arithmetic Logic Unit                          |

|-------|----------------------------------------------------|

| ASIC  | <br>Application Specific Integrated Circuit        |

| ASIP  | <br>Application Specific Instruction set Processor |

| BRAM  | <br>Block RAM                                      |

| CAD   | <br>Computer Aided Design                          |

| CLB   | <br>Configurable Logic Block                       |

| CPLD  | <br>Complex PLD                                    |

| CPU   | <br>Central Processing Unit                        |

| DCM   | <br>Digital Clock Manager                          |

| DRAM  | <br>Dynamic RAM                                    |

| DSP   | <br>Digital Signal Processing                      |

| FIFO  | <br>First In First Out                             |

| FIR   | <br>Finite Inpulse Response                        |

| FPGA  | <br>Field Programmble Gate Array                   |

| GMO   | <br>Global Memory Object                           |

| GPP   | <br>General Purpose Processor                      |

| HDL   | <br>Hardware Description Language                  |

| HDTV  | <br>High-Definition Television                     |

| HLL   | <br>High Level programming Language                |

| IIR   | <br>Infinte Impulse Ressponse                      |

| IMEM  | <br>Interface and Memory Modeling                  |

| IΡ    | <br>Intellectual Property                          |

| IOB   | <br>Input/Output Block                             |

| LUT   | <br>Look Up Table                                  |

| MMX   | <br>Multimedia Extension                           |

| PLD   | <br>Programmble Logic Device                       |

| RAM   | <br>Random Access Memory                           |

| RISC  | <br>Reduced Instruction Set Computer               |

| RTL   | <br>Register Transfer Level                        |

| RTVPS | <br>Real-Time Video Processing System              |

| SIMD  | <br>Single Instruction Multiple Datapath           |

| SLWC  | <br>Sliding Window Controller                      |

| SRAM  | <br>Static RAM                                     |

| UML   | <br>Unified Modelling Language                     |

| VHDL  | <br>VHSIC HDL                                      |

| VHSIC | <br>Very-High-Speed Integrated Circuits            |

| VIP   | <br>Video/Image Processing                         |

| VLIW  | <br>Very Large Instruction Word                    |

| VLSI  | <br>Very Large Scale Integration                   |

| -     | <br>, 0                                            |

### **LIST OF FIGURES**

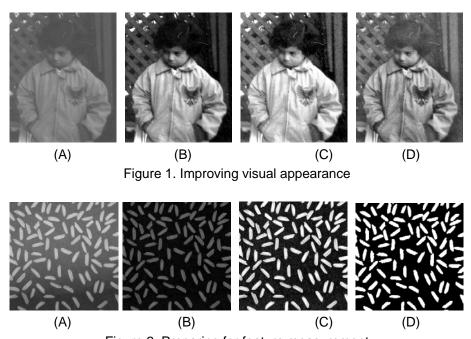

| Figure 1. Improving visual appearance                                        | 2     |

|------------------------------------------------------------------------------|-------|

| Figure 2. Preparing for feature measurement                                  | 2     |

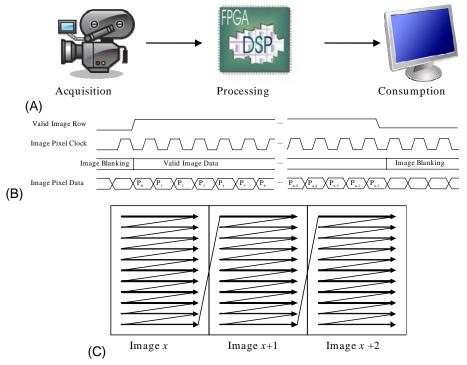

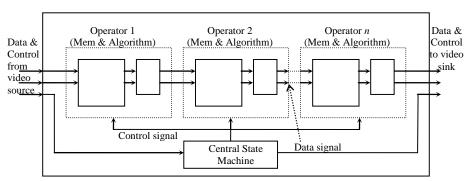

| Figure 3. Video processing system                                            | 3     |

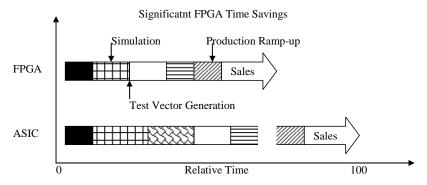

| Figure 4. Time-to-Market - FPGAs vs. ASICs [14]                              | 5     |

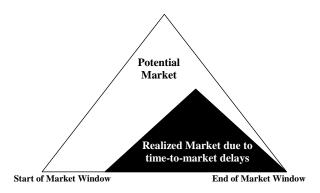

| Figure 5. Product time-in-market [14]                                        | 5     |

| Figure 6. Signal processing implementation spectrum [15].                    | 6     |

| Figure 7. Comparison of various implementation platforms [8]                 | 6     |

| Figure 8. Neighbourhood oriented image processing                            | 7     |

| Figure 9. Spatial temporal oriented image processing                         | 8     |

| Figure 10 Circular buffers as line buffers.                                  | 10    |

| Figure 11 Block-RAM data flow at read first operation.                       | 10    |

| Figure 12 Resource usage on FPGA                                             | 12    |

| Figure 13 Resource usage on DSP                                              | 13    |

| Figure 14 Performance                                                        | 13    |

| Figure 15. Power consumption                                                 | 13    |

| Figure 16. Overview of Xilinx Spartan 3 [48]                                 | 16    |

| Figure 17. Xilinx Spartan 3 CLB [48]                                         | 16    |

| Figure 18. FPGA Interconnects                                                | 17    |

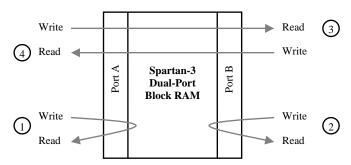

| Figure 19. RAM data path [50]                                                | 19    |

| Figure 20. Spartan 3 MicroBlaze embedded processor [54].                     | 20    |

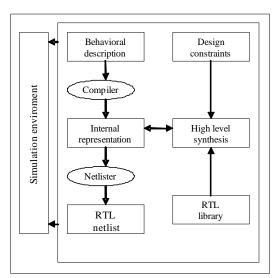

| Figure 21. Design Flow for implementing custom applications on FPGA          | 25    |

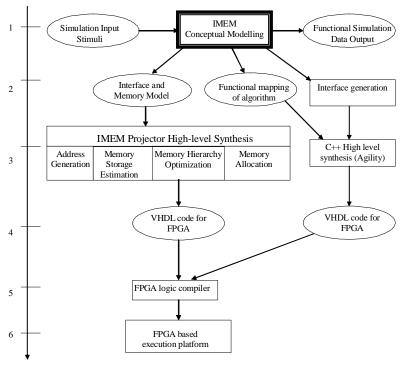

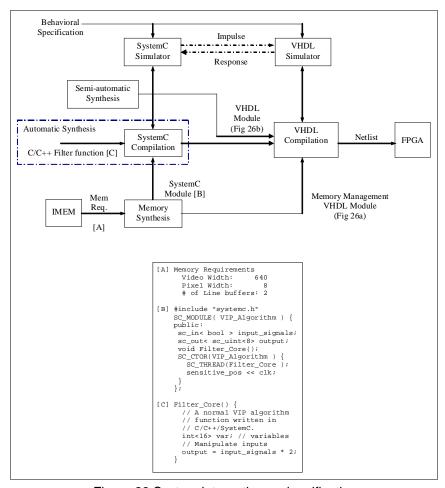

| Figure 22. System synthesis workflow.                                        | 32    |

| Figure 23 System integration and verification.                               | 33    |

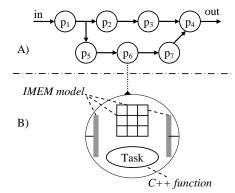

| Figure 24. IMEM model of a video processing system.                          | 35    |

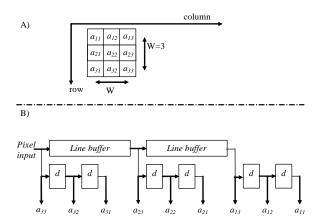

| Figure 25 A: Spatio-temporal neighbourhood of pixels. B: Memory architecture | cture |

| for a single image processing operation.                                     | 35    |

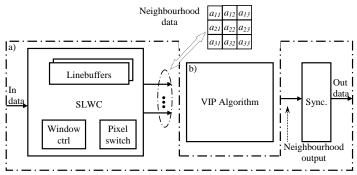

| Figure 26 Boundary conditions implementation architecture.                   | 36    |

| Figure 27 Neighbourhood oriented system.                                     | 36    |

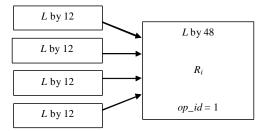

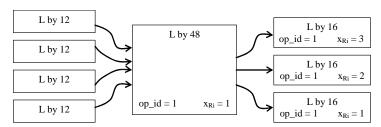

| Figure 28 Global Memory Object formation                                     | 37    |

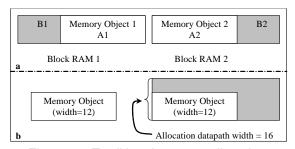

| Figure 29. Traditional memory allocation.                                    | 38    |

| Figure 30. Proposed memory allocation.                                       | 39    |

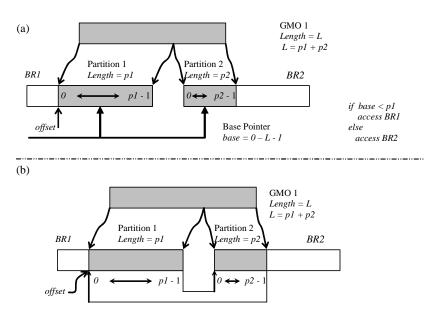

| Figure 31. Partitioning global memory object.                                | 41    |

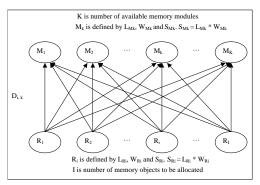

| Figure 32. Allocation model.                                                 | 42    |

| Figure 33. The proposed allocation algorithm.                                | 42    |

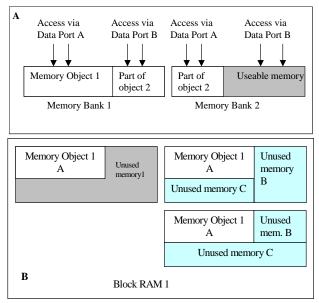

| Figure 34 Architecture driven memory allocation                              | 46    |

| Figure 35 Two memory accessing approaches                                    | 47    |

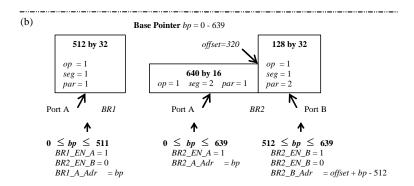

| Figure 36. Base Pointer Approach.                                            | 48    |

| Figure 37. Distributed Approach.                                             | 49    |

| Figure 38. Constraint generation algorithm                                   | 52    |

| Figure 39. Clock distributions showing the effect of constraints             | 52    |

| Figure 40. Constraint generation workflow                                    | 53    |

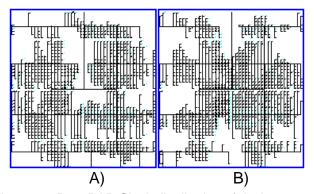

| Figure 41. Memory allocation of Case 2-1 on Xilinx Spartan 2E FPGA.          | 56    |

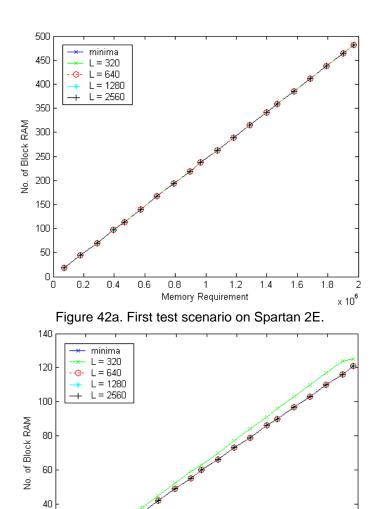

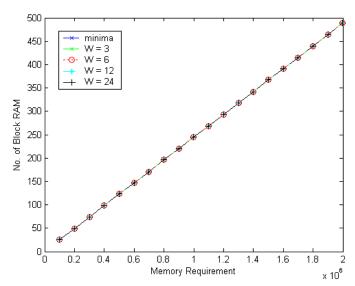

| Figure 42a. First test scenario on Spartan 2E.                               | 57    |

| Figure 43a. Second test scenario on Spartan 2E.                              | 58    |

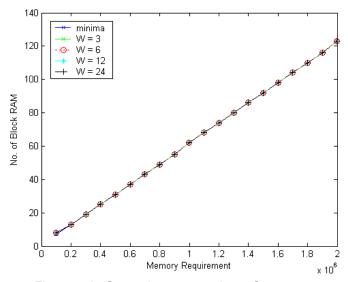

| Figure 44. Block RAM usage with varying memory requirements | 60 |

|-------------------------------------------------------------|----|

| Figure 45. Memory usage                                     | 63 |

| Figure 46. Post-PAR Clock distribution of design case 2     | 63 |

| Figure 47. Relationship between thesis papers.              | 67 |

### **LIST OF TABLES**

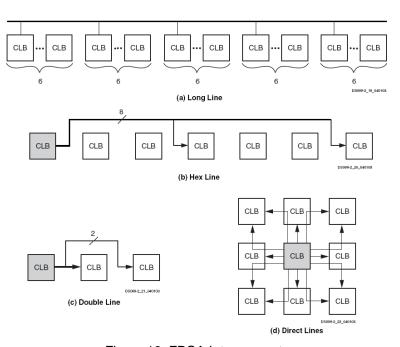

| Table 1. Summary of FPGA inter-connects                   | 18 |

|-----------------------------------------------------------|----|

| Table 2. Memory requirement of considered design cases    | 54 |

| Table 3. Allocation result of the algorithm on Spartan 2E | 54 |

| Table 4. Allocation result of the algorithm on Spartan 3  | 54 |

| Table 5.Average allocation results for all cases          | 61 |

| Table 6. Allocation on Spartan II                         | 61 |

| Table 7. Allocation on Spartan III                        | 61 |

| Table 8. Comparison of the two approaches                 | 63 |

| Table 9. Resource usage summary                           | 65 |

| Table 10. Dynamic power consumption                       | 66 |

| Table 11. Authors' Contributions                          | 70 |

#### **LIST OF PAPERS**

This thesis is mainly based on the following five papers, herein referred to by their Roman numerals:

## Paper I RAM Allocation Algorithm for Video Processing Applications on FPGA,

Najeem Lawal, Benny Thörnberg, Mattias O'Nils and Håkan Norell.

Accepted for publication in *Journal of Circuits, Systems and Computers.*, Vol. 15, No. 5, October 2006.

#### Paper II Address Generation for FPGA RAMs for Efficient

Implementation of Real-Time Video Processing Systems,

N. Lawal, B. Thörnberg, M. O'Nils,

Proceedings of the Conference on Field Programmable Logic and Applications, Tampere, Finland, 2005, pp. 136 - 141. ISBN 0-7803-9362-7

# Paper III Embedded FPGA Memory Requirements for Real-Time Video Processing Applications

Najeem Lawal and Mattias O'Nils,

Proceedings of the 23rd Norchip Conference, Oulu, Finland

November 2005, pp. 206 - 209.

ISBN 1-4244-0064-3

### Paper IV Automatic Generation of Spatial and Temporal Memory Architectures for Embedded Video Processing Systems,

H. Norell, N. Lawal and M. O'Nils,

In European Association for Signal and Image Processing

(EURASIP) Journal on Embedded Systems, Volume 2007, 2007.

## Paper V C++ based System Synthesis of Real-Time Video Processing Systems targeting FPGA Implementation,

N. Lawal, B. Thörnberg and M. O'Nils,

Proceeding of the 21th International Parallel and Distributed Processing Symposium (IPDPS 2007), 26-30 March 2007, Long Beach, California, USA.

## Paper VI Power-aware Automatic Constraint Generation for FPGA Based Real-Time Video Processing Systems

N. Lawal, B. Thörnberg and M. O'Nils,

Proceedings of the 25th IEEE Norchip Conference, Aalborg

Denmark November 2007, pp. 1 - 5.

ISBN: 978-1-4244-1516-8

# Paper VII Architecture driven memory allocation for FPGA Based Real-Time Video Processing Systems

N. Lawal, B. Thörnberg and M. O'Nils, Submitted to Journal of Embedded Hardware Design.

Related papers not included into this thesis:

Evaluation of embedded RAM characteristics for FPGA implementation of real-time image processing systems, J. Rojas, N. Lawal and M. O'Nils, Study report

Comparison of FPGA and DSP performances in neighbourhood oriented real-time video processing Najeem Lawal, Study report

C++ based System Synthesis of Real-Time Video Processing Systems targeting FPGA Implementation, M. O'Nils, B. Thörnberg and N. Lawal,

In Proceeding of FPGAworld Conference, Nov 2007.

#### 1 INTRODUCTION

This thesis is concerned with memory synthesis in the implementation of real-time video processing systems on field programmable gate arrays. This memory synthesis considers memory architecture, allocation, accessing, power optimisation and constraint generation. Our interest in memory synthesis is to provide an easy to use high-level design tool for managing the data required in real-time video processing systems. This interest originates from the fact that implementing memory for required data is extremely taxing, the available memory is limited and the current memory synthesis methodologies do not offer a cost-effective use of the limited memory. To present this thesis, we will first present the essential background to a real-time video processing system in Section 1.1. Section 1.2 presents four alternatives for implementing real-time video processing systems. In Section 1.3 we will identify sources for the data requirement in video processing and the motivation behind this work. We present the contribution of this thesis in Section 1.4. Finally, in Section 1.5 we will present the outline of this thesis.

#### 1.1 REAL-TIME VIDEO PROCESSING SYSTEM

Images represent an important part of information communication in everyday life. They are essential parts of the interaction between people, human-computer interaction and computer computation. Images are useful in reasoning, education, communication, navigation and analysis. Image processing can be described as a task which converts an input image into a modified output image or a task that extract information from the features present in an image. Image processing is used for two somewhat different purposes namely:

- 1. improving the visual appearance of images to the human viewer

- 2. preparing images for the measurement of the features and the structures present

Because these two purposes are different, the operations involved in them might also be different, but they do share many common operations. In general the

purpose of image processing is not to reduce data content (which might often be case when images are transformed from colour images to gray-scale images or from gray-scale images to binary) but to preserve and magnify the quality of the image. For visual enhancement, operations that facilitate human comprehension and that make images subjectively appealing are carried out. Examples of these operations include contrast adjustment, image smoothening and colourisation. The operations are useful in video entertainment, image printing, transmission and reproduction. Figure 1 shows different operations that can be applied to an original image (A) to make it visually appealing and comprehensible.

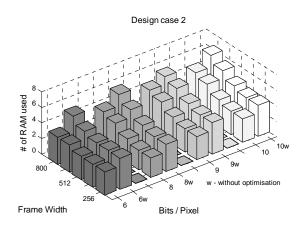

In image measurement, operations that cause the image features to be well defined and more pronounced through enhanced edges or uniform brightness for objective analysis and classification are carried-out. Examples of these operations include image segmentation, noise elimination and morphological erosion and dilation. These operations find applications in robot vision and machine vision. Figure 2 shows operations that can be applied to an input image to make the counting of the features in the image easier and autonomous by a computer.

Figure 2. Preparing for feature measurement

The effectiveness of image processing operations affect the complexity of the subsequent stages of image usage such as image compression and de-compression, image storage and retrieval and, image transmission. Thus image processing operations will continue to play a major role in the hand-held, battery-power mobile devices for video conferencing, video telephony and robot vision. This is because an excellently processed, feature enhanced and error free image will

greatly simplify a coding algorithm and provide better use of storage spaces and transmission bandwidth.

Video processing is essentially image processing in which the time domain is considered. This means that it might be necessary to register and process temporal changes in the image content. Figure 3A shows a typical set-up of a video processing system. The set-up includes an image acquisition device (the camera), the image processing unit (the processor) and an information consumption unit (the display). Of course, it is possible to have other components such as light sources, storage devices, human observers and communication devices based on applications. We will however focus on the essential aspects of image processing. Figure 3B shows the relationship between a single picture element (pixel) and an image whereas Figure 3C depicts the relationship between images and video. At the lowest level of operation, video processing involves the processing of each pixel in an image and image after image through-out the video stream.

Figure 3. Video processing system

Real-Time Video Processing System (RTVPS) is the term used to describe a class of video processing system in which the video signal is processed at the rate of video capture such that the rate of generating output pixels matches the rate of receiving input pixels. Hence there is a throughput of one pixel per clock cycle. Thus after an initial delay, the system enters a state during which a pixel is being

received at the input side and, at the same time, a pixel is being produced at the output side. This does not, however, imply that this output pixel is the result of the newly received input pixel since there would be delays due to data buffering and pipelines in the computation.

#### 1.2 IMPLEMENTATION ALTERNATIVES

In the following sub-sections, we will present four major alternatives for implementing RTVPS namely 1) general purpose processors, 2) application specific instruction-set processors, 3) field programmable gate arrays and 4) application specific integrated circuits. In general, implementation platforms can be classified as general purpose and applications specific from functionality point of view or they can be classified as reconfigurable or non-reconfigurable from programmability point of view.

#### 1.2.1 Application Specific Integrated Circuits

Application Specific Integrated Circuits (ASICs) are fabricated and tailor-made for special or dedicated applications. This means that their precise functions and performance are considered and fully analyzed before fabrication. The consequence is efficiency, reliability and high performance. However, changes in system requirements which might be due to an oversight or a changing system demands results in a complete replacement of the device. In addition, unless market volume demand could really justify the manufacturing cost, the development costs for ASICs are a major set back. The trade-offs between performance and flexibility, which has an influence on the choice of computing devices, are presented in [1].

#### 1.2.2 Software Based Processors

General Purpose Processors (GPPs) and Application Specific Instruction-set Processors (ASIPs) are software based and highly reconfigurable. On these devices application programs are written in high level languages and executed within a processor. Due to the sequential nature of these programs, large overheads are involved in the instruction set generation, decoding and execution. This limits the performance and throughput of these devices thus leading to the development of many instruction set architectures, which includes, VLIW, SIMD and MMX [2]. The main objective is for performance improvements through parallelism, pipelining, caching, and concurrency. The literature has much information with regards to the specifics of these architectures and since it is not the focus of the paper detailed discussions will not be provided.

#### 1.2.3 Programmable Hardware Processors

In the hardware domain programmability can be achieved through the programmable gate-array or logic-devices which are commonly used. Depending on the capacity and architecture of the constituent basic elements, reconfigurable hardware can be categorized as programmable logic devices (PLD), complex PLD (CPLD) and Field Programmable Gate Array (FPGA). An overview of technology, architecture and programming tools for programmable hardware devices is presented in [5]. FPGA programmability enables hardware designers to greatly reduce the overall product time-to-market as shown in Figure 4.

Figure 4. Time-to-Market - FPGAs vs. ASICs [14]

Other advantages of a programmable hardware solution include reduced development costs (minor non-recurring engineering costs), the possibility of rapid prototyping and the ability to support field upgrades and remote downloads that will extend the longevity of the product in the market (time-in-market) [14]. These are depicted in Figure 5. Hence according to Figure 5, the sooner that hardware designers market their products, the greater their income. This is one of the major advantages of FPGAs and explains why many applications, which have historically been implemented in software and/or ASIC, are now being developed as FPGAs [6], [7].

Figure 5. Product time-in-market [14]

The implementation of computationally intensive and data transfer dominated applications, which are common in RTVPS, has previously been

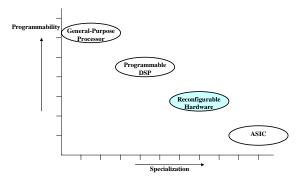

dominated by Digital Signal Processors (DSP) and dedicated application specific integrated circuits (ASIC). However, developments in FPGA have made it possible to implement RTVPS applications using FPGA [6], [7]. Figure 6 shows the implementation spectrum across computing devices. It should be noted that the different platforms in Figure 6 are not isolated as depicted in the figure but are over-lapping clouds. Figure 7 summaries the characteristics of the four platforms discussed above. From this comparison it is obvious that FPGA provides a reasonable performance alternative for image/video processing in real-time with the possibilities of re-programmability with evolving application specifications. For this reason FPGA has been chosen as the implementation platform for RTVPS. The following sections will focus on a detailed discussion on the FPGA technology.

Figure 6. Signal processing implementation spectrum [15].

| Technology | Performance<br>/ cost | Time to<br>market | Time to change code functionality | Power<br>Consumption |

|------------|-----------------------|-------------------|-----------------------------------|----------------------|

| ASIC       | Very High             | Very Long         | Impossible                        | Low                  |

| FPGA       | Medium –<br>High      | Long              | Long                              | Low – Medium         |

| ASIP       | Medium                | Medium            | Medium                            | Medium – High        |

| GPP        | Low –<br>Medium       | Very Short        | Very Short                        | High                 |

Figure 7. Comparison of various implementation platforms [8]

#### 1.3 DATA REQUIREMENTS IN RTVPS

In this thesis introduction, we will not deal with discussions related to image acquisition such as lighting and optical set-up, image sampling and quantization. We will also not dwell on discussions regarding post processing and image

consumption such as monitor display, information reporting or decision making from the results of image processing. The stages as represented in Figure 3A are important to the core processing but are not included in the scope of this thesis. Our concern is with the operations involved in image processing and the need for data storage in image processing. We note that image processing can be carried out in two domains namely

- 1. spatial domain image processing

- 2. frequency domain image processing

Spatial domain depends on raw image pixel data and direct manipulation of pixel whereas frequency domain processing is based on the Fourier or cosine transform of the image and the manipulation of the frequency components of the image data.

In spatial domain, image processing can be pixel-wise. This is referred to as point processing. It describes the operations that depend solely on the pixel value without any reference to the values of the surrounding pixels. This type of operation may require pixels from two image sources or an image source and a transformation function. Examples of this type of processing include image negation, image addition and subtraction, thresholding and histogram equalisation.

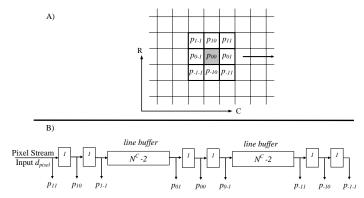

In addition, spatial domain image processing can be in the form of neighbourhood processing. It describes operations in which the values of a group of pixels in an input image are required to compute only one pixel in the output image. This type of processing may require a processing mask or kernel which defines the operation. Examples of this type of processing include statistical operations such as the mean, median, maximum and minimum, convolutions operations such as a Laplacian filter, edge detection and a morphological operation. Figure 8 shows an example of neighbourhood based image processing and the data registers required to compute an output pixel. It also shows the need for buffer in order to have the appropriate set of pixel data.

Figure 8. Neighbourhood oriented image processing

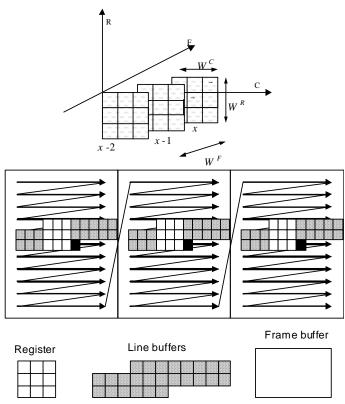

Furthermore, image processing can be temporal processing and is essentially neighbourhood processing in which the image data is extracted from more than one image frame. As with neighbourhood processing the computation produces only pixel data for all the input pixel data. An example of this type of image processing includes cubic median filter. Figure 9 shows a spatial temporal neighbourhood of 27 pixels from 3 frames. For this image processing operation, we will require 27 registers, 6 row buffers and 2 frame buffers.

Figure 9. Spatial temporal oriented image processing

In general, it is common that in a typical RTVPS the majority of the operations are neighbourhood oriented and thus has the requirement for the buffers for the necessary neighbourhood pixel data (Figure 8 and Figure 9). A neighbourhood of pixels constitutes a set of pixel data from which an RTVPS operator in the processing algorithm calculates an output pixel corresponding to the neighbourhood's central pixel. The neighbourhood is built around each pixel in the input image in order to generate an output image. The consequence is that a large number of data buffers (line- and frame-buffers) are required which is, in turn, dependent on the size of the video frame and the operation window in order to ensure that all the required pixel data for each operation are available. Line

buffers are used to store rows of pixels in the spatial neighbourhood. A spatial neighbourhood normally has dimensions of M-by-N, where M and N are odd values such that the central pixel is symmetrical about any axis. N and M denote the height and width of the spatial neighbourhood and usually determines the number of line buffers and delay elements required by the spatial neighbourhood operator. Frame buffers are used to store images in the temporal neighbourhood. A temporal neighbourhood normally has dimensions of L-by-M-by-N where M and N are defined as above and L, also an odd value, denotes the temporal depth of the neighbourhood. L determines the number of frame buffers in the temporal neighbourhood. Line buffers are usually allocated to on-chip memories while external memories are required for frame buffers. The size of each element in these buffers depends on the dynamic range of the video signal. Hence a 5-by-5 spatial neighbourhood requires four line buffers while two line buffers are required by a 3-by-3 neighbourhood. In the temporal domain, a neighbourhood of seven frames will require six frame buffers. An efficient data management tool is required since memory access generally constitutes major bottlenecks.

#### 1.4 MOTIVATION FOR EFFICIENT MEMORY SYNTHESIS

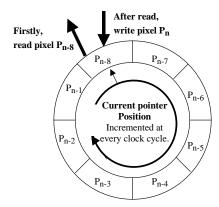

If a simple RTVPS application is considered involving only a spatial domain, for example a Sobel Operator for detecting edges in a video frame, then a neighbourhood (3-by-3) would be built around each pixel in the frame. Building such a neighbourhood requires the data of the necessary pixels to be stored. Figure 8 depicts such a neighbourhood where,  $p_{ij}$  represents the pixel data at the *i*-th column and j-th row in the neighbourhood,  $d_{pixel}$  is the pixel data entering the neighbourhood as the processing window traverses all the pixels in the image and d is a clock delay. Line buffers are required to store this pixel data in order to create the neighbourhood. In Figure 8b, these buffers are represented as a line buffer. A line buffer can be thought of as a First-In-First-Out shift register (FIFO) with pre-determined constant length - that can be implemented as a circular buffer allocated to a set of memory locations. The example in Figure 10 depicts a set of eight memory locations, n-8 to n-1, which are indexed by a pointer in a modulus-8 order. For every pointer position, pixel data  $P_{n-8}$  is firstly read and then pixel data Pn is written. The Xilinx block-RAM has the attractiveness of allowing this firstread-then-write operation to execute in one single clock cycle.

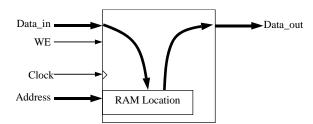

Figure 11 depicts a Xilinx block-RAM for one of the two ports at a read-first-then-write operation. This memory has two synchronous independent access ports. Both ports have the set of signals shown in Figure 11. Data\_in and Data\_out are input- and output data busses. These busses are latched on the rising or falling clock edge, depending on the configuration. WE enables a write operation to the memory location, pointed to by Address, after that a read operation is performed. This feature allows a memory location to be both read and written at the same clock cycle using one single port. In addition, the dual independent ports enable

two FIFOs to be allocated to one block-RAM without serializing the memory accesses. This explains why we do not consider scheduling effects in our memory allocation optimization model.

Figure 10 Circular buffers as line buffers.

Figure 11 Block-RAM data flow at read first operation.

The management of the line-buffers (memory objects) identified in Figure 8 and Figure 9 is the focus of this work. The main goal is to develop an automatic memory synthesis tool that makes the most efficient use of the addressable memory locations available in all of the instantiated embedded memory before instantiating another.

#### 1.5 PROBLEM DESCRIPTION

The method of allocating the line buffers identified in Figure 8 and Figure 9 to the embedded memory greatly affects the use of the memory depending on the size of the on-chip memory. In addition, the length of the line buffer and the bitwidth of each of the elements in the line buffer also affects the efficiency of the allocation. Increasing the neighbourhood dimension, in terms of the number of frames, *L*, the width of the video frame, *M* and number of line buffers, *N* as well as the number of operators in the RTVPS application leads to increasing complexities

in data management. In general, managing the data required in such a neighbourhood leads to four major problems namely:

- 1. Data allocation problems due to pixel-width and video-resolution (when the bit-width of each element in a line buffer and its length are not directly supported for optimised allocation)

- 2. Data management problems with the increasing number of line buffers, *N*

- 3. Data management problems caused by with the increasing number of RTVPS operators and number of frames, *L*

- 4. Power consumption problem due to complex data routing

These problems will be discussed at a later stage in the thesis (Section 4.5).

#### 1.6 Performance Comparison

In Section 1.2, we discussed possible implementation alternatives for real-time image processing. In Section 1.3 we identified the memory requirements typical in RTVPS and provided the motivation behind the requirement for the efficient allocation of the memories in Section 1.4. Section 1.5 presented problems that may arise during the allocation of these memories. By using the problem presented in Section 1.5 as the performance index we will in this section compare two of these alternatives from Section 1.2 namely DSP and FPGA. We chose these two because they are both reconfigurable and are targeted as being effective for the specific application area.

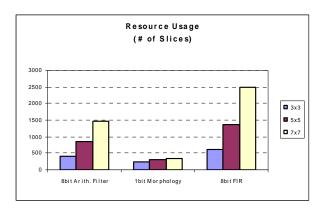

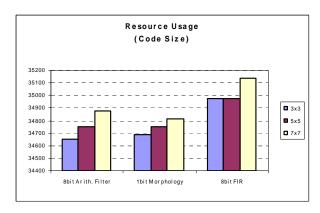

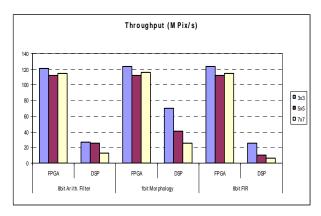

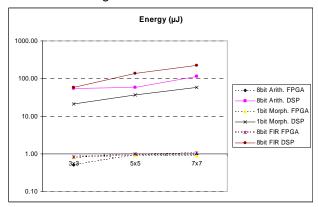

The objective of these experiments is to find the relationship between the power consumption, performance and resource usage on FPGA and DSP and the size of the neighbourhood window required in real-time video processing systems. The experiments were conducted under three scenarios, namely, 1-bit morphology erosion, 8-bit average filter and 8-bit convolution filter. These filters are typical examples of neighbourhood oriented operation. For the convolution filters, we assumed 8-bit mask values. For these scenarios three neighbourhood sizes (3x3, 5x5 and 7x7) were used. For simplicity, we chose neighbourhoods with square dimensions. For these experiments, input video streams with 640-by-480 frame resolution were used.

#### 1.6.1 Experimental Set-Up

The experimental set-up for the FPGA is as follows, we implemented the architecture in Figure 26 and the video processing filters for the different neighbourhood sizes. We assumed the input video stream is limited by the FPGA performance rather than the camera. The implementation was synthesised using the Xilinx Integrated Software Environment software version 8.1i in order to obtain the post-place and route resource usage and performance. The Xilinx XPower software was used to calculate the power consumption per clock cycle.

The experimental set-up for DSP is as follows, we assume the TMS320C6418 DSP runs at 600MHz and that the input data stream is at 10 MPixels/s thus lower reducing the CPU utilization and power consumption. Since our implementation avoids boundary conditions by increasing the image size, we assume perfect cache hits, local memory allocations for all the line-buffers, and one data read for the newest neighbourhood pixel and one memory write for the newly computed data corresponding to the central pixel in the output image. Using Texas Instrument Code Composer Studio software version 2.10, we were able to profile and achieve performances closer to the benchmarks values [96].

#### 1.6.2 Results

Figure 12 - Figure 15 show the results obtained. It should be noted for the performance figures, that as long as there are available resources on the FPGA, the performance for the system will be the same regardless of the number of active operators. For the DSP the performance (samples per second) will decrease when additional functionality is added to the system. Thus, the performance numbers are somewhat biased towards the DSP. The energy figures are also fairer in a comparison between the two architectures. The results show that for this class of operations, with optimized memory allocation and the accessing method presented in this thesis, and full parallel and pipeline operations, FPGA achieves a better performances in between 2.0 to 8.7 in terms of throughput and an average reduced energy consumption of 80 times per sample. It should be noted for the performance figures, that as long as there are resources available on the FPGA, the performance for the system will be the same regardless of the number of active operators. For the DSP the performance (samples per second) will decrease when additional functionality is added to the system. Thus, this means that the performance numbers are somewhat biased towards the DSP. The energy figures are fairer in a comparison between the two architectures.

Figure 12 Resource usage on FPGA

Figure 13 Resource usage on DSP

Figure 14 Performance

Figure 15. Power consumption

#### 1.6.3 Conclusion

This experiment shows that implementing applications on FPGA can take advantage of the application's specific memory requirements in order to develop

optimised memory architecture which when combined with the possibilities of optimised memory allocation and accessing and full parallel and pipeline operations, will make FPGA achieve a better performance by about 2.0 to 8.7 in terms of throughput and an average of 80 times lower energy consumption per sample over DSP.

#### 1.7 MAIN CONTRIBUTIONS

The main contribution in this thesis is to provide solutions to the problems identified in Section 1.5. The following solutions are offered to the problems:

- 1. Memory architecture organizing the data required by the RTVPS operator.

- 2. Memory allocations and accessing

- 3. Interfaces to data required by operators in a temporal neighbourhood

- 4. Low power optimization

- 5. High-level interface for describing the required memories and generation hardware implementation.

These solutions will be discussed at a later stage together with the results obtained by their use. Tests on the performance of the solutions and comparisons with other works are also discussed.

#### 1.8 THESIS OUTLINE

The next section presents the developments and trends within FPGA with the focus on embedded memory and DSP core. Earlier research works relating to on-chip memory allocation, memory addressing, power management and constraint generation are presented in Section 3. Section 4 presents the contribution of this research and the connections between this research and other high-level design tool for real-time video processing systems are also presented in addition to the experimental results and performance analysis under increasing RTVPS complexity and FPGA technology. Section 5 summarises the work covered by all the papers included in this thesis. The papers, which represent original contributions to this research work, are presented in the appendices. Section 6 summarises and concludes the contribution of this thesis.

#### 2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)

FPGAs have been employed in implementing high-performance computations such as fuzzy logic controller, [37], complex Monte Carlos and percolation problem simulations [38]. In [6], an FPGA was used for face tracking in streaming video using a Radial Basis Function (RBF) neural network for real-time verification. The literature is exhaustive with regards to the use of FPGAs for network monitoring, audio/video signal processing and safety critical applications. These are the application areas previously dominated by DSP. The attractions for implementing these applications on FPGAs can be traced to those features that distinguish them from other computing platforms. These features are listed as follows [39]

- On-chip RAM blocks and distributed memories

- Embedded processors

- Dedicated computational units (multipliers and DSP block)

- Programmable logic cells

- Programmable interconnect

- Programmable Input/Output cells

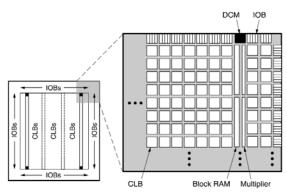

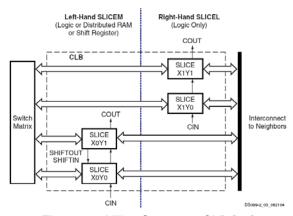

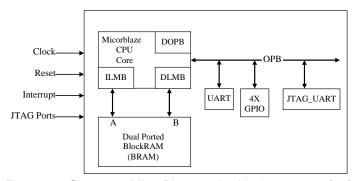

Although specific implementation details vary among the vendors, the focus here is on the low-cost Xilinx Spartan 3 [48] and additionally, the features common to the FPGA vendors are presented in detail. Figure 16 shows the architectural overview of Xilinx Spartan 3. In the figure, DCM, IOB and CLB represent Digital Clock Manager, Input/Output Blocks and Configurable Logic Blocks respectively. The remaining part of this section will discuss the list above.

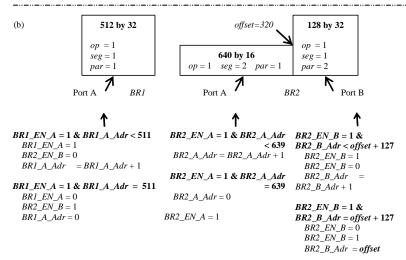

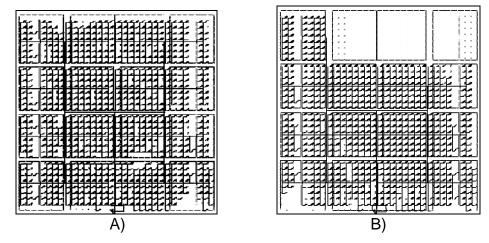

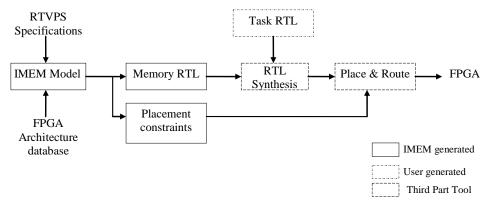

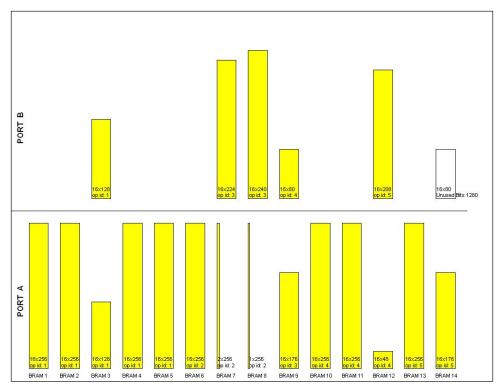

#### 2.1.1 Programmable Logic Cells